## Advantages of PLL Circuitry in Altera **Devices**

TECHNICAL BRIEF 10

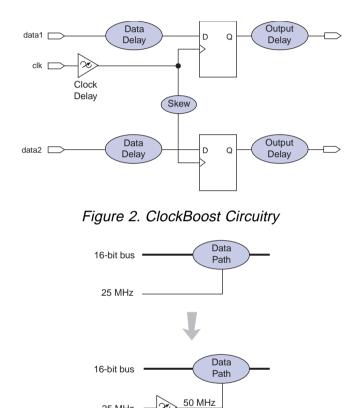

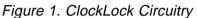

Altera is offering two new features for high-density PLDs-called ClockLock and ClockBoost-that use a phase-locked loop (PLL). The ClockLock feature minimizes on-chip clock skew, significantly increasing performance. The ClockBoost feature increases clock frequencies by as much as four times the incoming clock rate, improving system bandwidth. Together, these enhancements provide significant breakthroughs in system performance and bandwidth. See Figures 1 and 2.

The revolutionary ClockLock and ClockBoost features greatly reduce clock delay, clock skew, and data delay within a device as shown in the following equations. Since larger devices tend to have longer delays and greater skew, PLL circuitry is especially important for high-density devices, such as the EPF10K100, the largest member of the FLEX 10K family. The benefits to customers are increased PLD performance and utilization.

25 MHz

$t_{co} = \operatorname{clock} \operatorname{delay} + \operatorname{clock} \operatorname{skew} + \operatorname{register} \operatorname{delay} + \operatorname{output} \operatorname{delay}$  $t_{SU}$  = register set-up + data delay - clock delay 0 0

M-TB10-PLL-01

**JULY 1996**

## **ClockLock: Faster System Performance**

The ClockLock feature uses the PLL to minimize on-chip clock skew, significantly improving performance. For example, by using the ClockLock circuitry in FLEX 10K devices, designers should see a worse case  $t_{SU}$  and  $t_{CO}$  of 6 ns and 3.6 ns, respectively, which would increase the expected system performance by more than 60%. This type of performance increase will help designers meet the high-speed bus interface requirements of the future. See Table 1.

| Timing<br>Parameter | Without<br>ClockLock<br>(Preliminary) | With ClockLock<br>(Preliminary) |  |

|---------------------|---------------------------------------|---------------------------------|--|

| t <sub>co</sub>     | 11.5 ns                               | 8.5 ns                          |  |

| t <sub>su</sub>     | 7.0 ns                                | 3.6 ns                          |  |

| f <sub>sys</sub>    | 54 MHz                                | 83 MHz                          |  |

Table 1. EPF10K100-3 Timing Comparison

## **ClockBoost: Increased System Bandwidth & Reduced Area**

The ClockBoost feature uses the PLL for clock multiplication, significantly reducing the logic resources required to implement functions. This reduction in gate requirements is achieved through a technique called time-domain multiplexing. For example, a design that requires a 32-bit data path function running at 40 MHz can be implemented with a 16-bit data path function running internally at 80 MHz, achieving the same functionality with half the logic resources and I/O requirements. See Table 2.

Table 2. Reduced Logic Resource Requirements Achieved via ClockBoost in the EPF10K100

| Circuit          | Without<br>ClockBoost<br>(LEs) | With ClockBoost<br>(LEs) |

|------------------|--------------------------------|--------------------------|

| 8 x 8 Multiplier | 330                            | 198                      |

In cases where time-domain multiplexing is not needed, designers can use a slower external system clock, and internally multiply it for use within the Altera PLD. The advantage in a slower system clock is simpler PCB design, as there would be less ringing on the clock traces.

## Altera: The PLL Leader

Altera is the only PLD vendor that offers devices with a PLL, as shown in Table 3. The ClockLock and ClockBoost features will be available in the Altera FLEX 10K and MAX 7000S families of high-density programmable logic devices.

| Device Density (Gates) | Altera                | AMD | Lattice | Lucent | Xilinx |

|------------------------|-----------------------|-----|---------|--------|--------|

| 0 – 25,000             | MAX 7000S<br>FLEX 10K | -   | -       | _      | _      |

| 25,000 - 50,000        | FLEX 10K              | _   | _       | _      | —      |

| 50,000 - 100,000       | FLEX 10K              | _   | _       | _      | _      |

Copyright © 1996 Altera Corporation. Altera, ClockLock, ClockBoost, FLEX, FLEX 10K, MAX, MAX 7000S, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Other brands or products are trademarks of their respective holders. The specifications contained herein are subject to change without notice. All rights reserved.